# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

DS3002-2 0

## VP101

### 30/50MHz 8-BIT CMOS VIDEO DAC

The VP101 is a CMOS 8-bit video DAC designed for use in high performance, high resolution colour graphics applications.

The device uses video control inputs (BLANK, SYNC and REF WHITE) to provide the VP101 with the video pedestal levels required to generate RS-343A compatible video signals into a doubly-terminated 75 $\Omega$  load, or alternatively to produce RS-170 video signals across a singly-terminated 75 $\Omega$  load.

Data and control inputs are fully pipelined to maintain synchronisation between the DAC outputs.

The full scale output current is defined by a 1.2V reference and a single resistor. The reference voltage is included on-chip in the VP101, but may be supplied externally if required (see Fig. 2).

Differential and integral linearity errors of the D-A converters are guaranteed to be a maximum of  $\pm 1LSB$  over the full operating temperature range.

#### **FEATURES**

- 30/50MHz Pipeline Operation

- Triple 8-Bit D-A Converters

- ±1 LSB Differential Linearity Error

- ±1 LSB Integral Linearity Error

- Guaranteed Monotonic

- RS-343A/RS-170 Compatible Levels

- Drives Doubly Terminated 75Ω Load

- Single 5V Power Supply

- Typical Power Dissipation 500mW

- Direct Replacement for Bt101

- On-Chip Reference Available

#### **APPLICATIONS**

- High Resolution Colour Graphics

- CAE/CAD/CAM Applications

- Image Processing

- Video Reconstruction

- Instrumentation

#### **ORDERING INFORMATION**

VP101-3 BA DP (Commercial - Plastic DIL Package)

VP101-3 BA HP (Commercial - J-lead Package)

VP101-5 BA DP (Commercial - Plastic DIL Package)

VP101-5 BA HP (Commercial - J-lead Package)

VP101-3 BA GP (Commercial - Plastic Leaded Chip Carrier, Gullwing formed leads)

#### **ABSOLUTE MAXIMIM RATINGS** (Referenced to AGND)

DC supply voltage ( $V_{AA}$ ) -0.3 to +7V Digital input voltage-0.3 to  $V_{AA}$  +0.3V Analog output short circuit duration Indefinite Ambient operating temperature 0°C to +70°C Storage temperature range-55°C to +125°C

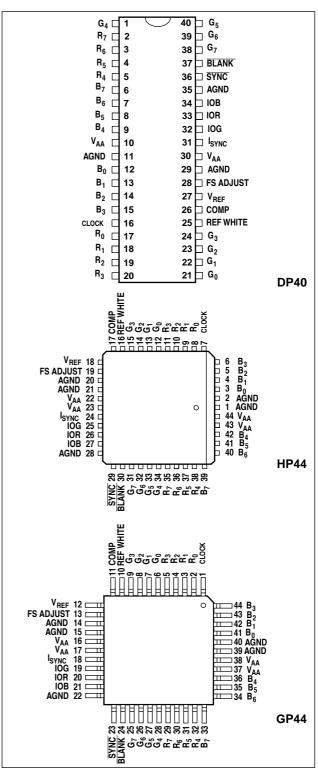

Fig.1 Pin connections (not to scale) - top view

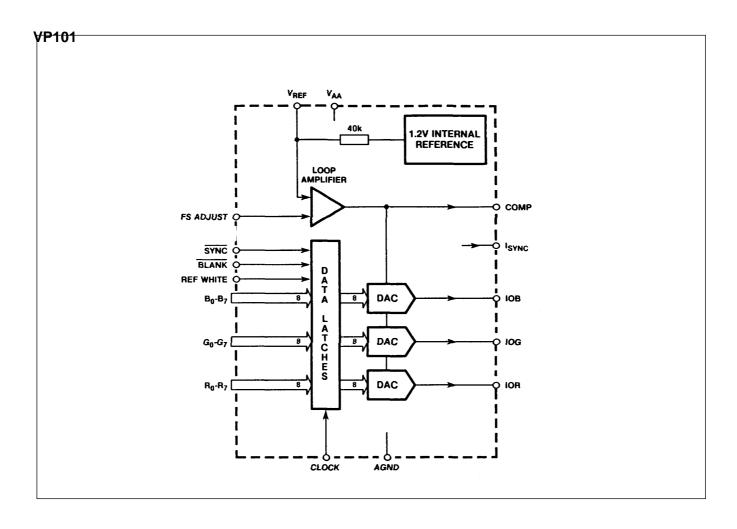

Fig.2 functional block diagram of VP101

#### **RECOMENDED OPERATING CONDITIONS**

| Parameter                                | Symb<br>ol       | Min. | Value<br>Typ. | Max. | Units | Conditions                           |

|------------------------------------------|------------------|------|---------------|------|-------|--------------------------------------|

| Supply voltage                           | V <sub>AA</sub>  | 4.75 | 5.00          | 5.25 | ٧     |                                      |

| Ambient operating temperature            | T <sub>amb</sub> | 0    |               | +70  | °C    |                                      |

| Output load                              | $R_L$            |      | 37.5          |      | Ω     |                                      |

| Reference voltage (internal or external) | V <sub>REF</sub> | 1.14 | 1.20          | 1.26 | V     | for RS-343A compatible output levels |

| FS ADJUST resistor                       | R <sub>SET</sub> |      | 542           |      | Ω     | J                                    |

#### THERMAL CHARACTERISTICS

DP HP GP

Thermal resistance, chip-to-case  $\theta_{jc}$  = 12 17 17 °C/W Thermal resistance, chip-to-ambient  $\theta_{jc}$  = 45 50 50 °C/W

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

As specified in recommended operating conditions.

DC CHARACTERISTICS

| Parameter                                                                                                                                                           | Symbol                                                | Min.            | Value<br>Typ.                     | Max.                                    | Units                                    | Conditions         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------------------------|-----------------------------------------|------------------------------------------|--------------------|

| Resolution (each DAC)                                                                                                                                               |                                                       | 8               |                                   |                                         | Bits                                     |                    |

| Accuracy (each DAC) Integral linearity error Differential linearity error Grey scale error Monotonicity                                                             | INL<br>DNL                                            |                 | ±0.3<br>±0.3<br>±1%<br>guaranteed | ±1<br>±1<br>±5%                         | LSB<br>LSB<br>% grey scale               |                    |

| Digital inputs Input high voltage Input low voltage Input high current Input low current                                                                            | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub> | 3.0<br>AGND-0.3 |                                   | V <sub>AA</sub> +0.3<br>1.2<br>+1<br>-1 | V<br>V<br>μΑ<br>μΑ                       | binary coding      |

| Analog outputs Grey scale current range                                                                                                                             |                                                       | 15              | 255                               | 20                                      | mA<br>LSB                                | )                  |

| Output currents White level relative to blank level                                                                                                                 |                                                       | 17.69           | 19.06<br>276                      | 20.40                                   | mA<br>LSB                                |                    |

| White level relative to black level                                                                                                                                 |                                                       | 16.74           | 17.62<br>255                      | 18.50                                   | mA<br>LSB                                |                    |

| Black level relative to blank level                                                                                                                                 |                                                       | 0.95            | 1.44<br>21                        | 1.90                                    | mA<br>LSB                                | tolerances assumed |

| Blank level on IOR, IOB                                                                                                                                             |                                                       | 0               | 5<br>0                            | 50                                      | mA<br>LSB                                | assumed            |

| Blank level on IOG                                                                                                                                                  |                                                       | 6.29            | 7.62<br>111                       | 8.96                                    | mA<br>LSB                                |                    |

| Sync level on IOG                                                                                                                                                   |                                                       | 0               | 5                                 | 50                                      | μΑ                                       |                    |

| LSB size DAC to DAC matching Output compliance External V <sub>REF</sub> input current Internal voltage reference Internal V <sub>REF</sub> temperature coefficient | USB  VOC IREF VREF                                    | -0.5<br>1.14    | 69.1<br>2<br>1.20<br>40           | +1.4<br>10<br>1.26                      | LSB<br>μΑ<br>%<br>V<br>μΑ<br>V<br>ppm/°C |                    |

#### **AC CHARACTERISTICS**

| Parameter                                                                                                     | Symbol                                                 | Min.         | VP101-<br>Typ.       | 5<br>Max. | Min.             | VP101-<br>Typ.       | 3<br>Max. | Units                          | Conditions                   |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------|----------------------|-----------|------------------|----------------------|-----------|--------------------------------|------------------------------|

| Max clock rate                                                                                                | f <sub>max</sub>                                       | 50           |                      |           | 30               |                      |           | MHz                            |                              |

| Data and control setup time<br>Data and control hold time                                                     | t <sub>SU</sub><br>t <sub>H</sub>                      | 6<br>2       |                      |           | 8<br>2           |                      |           | ns<br>ns                       |                              |

| Clock cycle time<br>Clock pulse width high time<br>Clock pulse width low time                                 | t <sub>CYC</sub> t <sub>CLKH</sub> t <sub>CLKL</sub>   | 20<br>8<br>8 |                      |           | 33.3<br>10<br>10 |                      |           | ns<br>ns<br>ns                 |                              |

| Analog output delay Analog output rise/fall time Analog output settling time Glitch energy Analog output skew | t <sub>DLY</sub><br>t <sub>VRF</sub><br>t <sub>S</sub> |              | 10<br>12<br>100<br>0 | 8         |                  | 10<br>15<br>100<br>0 | 9         | ns<br>ns<br>ns<br>pV-sec<br>ns |                              |

| Pipeline delay                                                                                                |                                                        | 1            | 1                    | 1         | 1                | 1                    | 1         | Clock                          |                              |

| V <sub>AA</sub> supply current                                                                                | I <sub>AA</sub>                                        |              | 120                  | 175       |                  | 100                  | 140       | mA                             | at $f_{max}$ , $V_{AA} = 5V$ |

#### **VP101**

#### **CIRCUIT DESCRIPTION**

As shown in the Fig. 2, the VP101 contains three 8-bit D-A converters, input latches, and a loop amplifier.

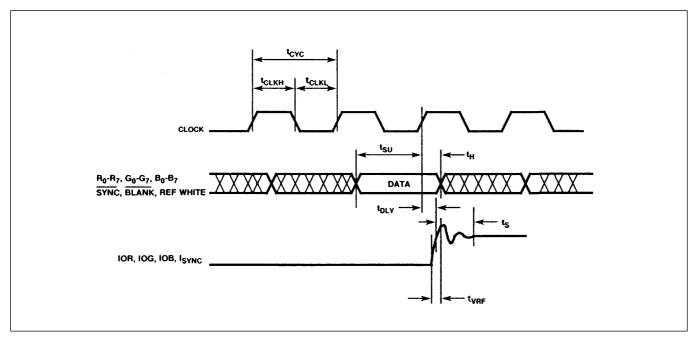

On the rising edge of each clock cycle, (see Fig. 4), 24 bits of colour information ( $R_0$ - $R_7$ ,  $G_0$ - $G_7$ , and  $B_0$ - $B_7$ ) are latched into the device and presented to the three 8-bit D-A converters. The REF WHITE input, also latched on the rising edge of each clock cycle, and will force the inputs of each D-A converter to \$FF.

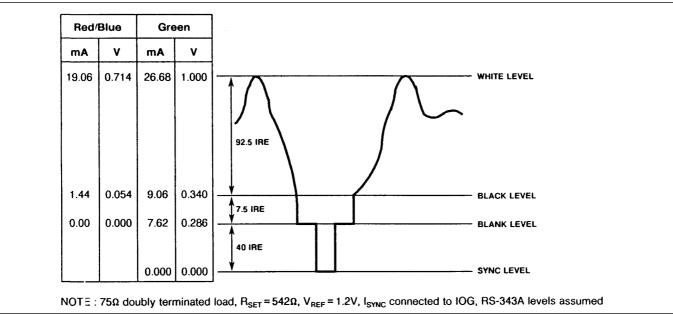

SYNC and BLANK are latched on the rising edge of the clock to maintain synchronisation with the colour data. These inputs add appropriately weighted currents to the analog outputs, producing the specific output levels required for video applications as shown in Fig. 3. Table 1 details how the SYNC, BLANK, and REFWHITE inputs modify the output levels.

The I<sub>SYNC</sub> current output is typically connected directly to the IOG output and is used to encode sync information onto the IOG output. If I<sub>SYNC</sub> is not connected to the IOG output, sync information will not be encoded on the green channel, and the IOR, IOG and IOB outputs will have the same full scale output current.

Full Scale output current is set by an external resistor (R<sub>SET</sub>) between the FS ADJUST pin and AGND.  $R_{SET}$  has a typical value of  $542\Omega$  for generation of RS-343A video into a 37.5 $\Omega$  load. The VP101 may be used in applications where an external 1.2V (typical) reference is provided, in which case the external reference should be temperature compensated and provide a low impedance output.

The D-A converters on the VP101 use a segmented architecture in which bit currents are routed to either the output or AGND by a sophisticated decoding scheme. This architecture eliminates the need for precision component ratios and greatly reduces the switching transients associated with turning current sources on or off. Monotonicity and low glitch energy are guaranteed by using identical current sources and current steering their outputs. An on-chip operational amplifier stabilises the full scale output current against temperature and power supply variations.

The analog outputs of the VP101 are capable of directly driving a  $37.5\Omega$  load, such as a doubly terminated  $75\Omega$  coaxial cable or interpolation filters.

Fig.3 Composite video output waveform

| Description | IOG<br>(mA) | IOR/IOB<br>(mA) | REF<br>WHITE | SYNC | BLANK | DAC<br>I/P Data |

|-------------|-------------|-----------------|--------------|------|-------|-----------------|

| White Level | 26.68       | 19.06           | 1            | 1    | 1     | \$XX            |

| White Level | 26.68       | 19.06           | 0            | 1    | 1     | \$FF            |

| Data        | Data + 9.06 | Data + 1.44     | 0            | 1    | 1     | Data            |

| Data-Sync   | Data + 1.44 | Data + 1.44     | 0            | 0    | 1     | Data            |

| Blank Level | 9.06        | 1.44            | 0            | 1    | 1     | \$00            |

| Blank-Sync  | 1.44        | 1.44            | 0            | 0    | 1     | \$00            |

| Blank Level | 7.62        | 0               | X            | 1    | 0     | \$XX            |

| Sync Level  | 0           | 0               | X            | 0    | 0     | \$XX            |

NOTE: Typical with full scale IOG = 26.68mA,  $R_{SFT}$  = 542 $\Omega$ ,  $V_{RFF}$  = 1.2V,  $I_{SYNC}$  connected to IOG

| Pin name                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLANK                                                                                              | Composite blank control input. A logic '0' forces the IOR, IOG and IOB outputs to the blanking level, as illustrated in Table 1. It is latched on the rising edge of CLOCK. When $\overline{\text{BLANK}}$ is a logic zero, the R <sub>0</sub> -R <sub>7</sub> , G <sub>0</sub> -G <sub>7</sub> , B <sub>0</sub> -B <sub>7</sub> , and REF WHITE inputs are ignored.                                                                                                                                                                         |

| SYNC                                                                                               | Composite sync control input. A logic '0' on this input switches off a 40 IRE current source on the I <sub>SYNC</sub> output. SYNC does not override any other control or data input as shown in Table 1; therefore it should be asserted only during the blanking interval. It is latched to the rising edge of CLOCK.                                                                                                                                                                                                                      |

| REF<br>WHITE                                                                                       | Reference white level control input. A logic '1' on this input forces the IOR, IOG and IOB outputs to the white level, regardless of the $R_0$ - $R_7$ , $G_0$ - $G_7$ and $B_0$ - $B_7$ inputs. It is latched on the rising edge of CLOCK. See table 1.                                                                                                                                                                                                                                                                                     |

| R <sub>0</sub> -R <sub>7</sub><br>G <sub>0</sub> -G <sub>7</sub><br>B <sub>0</sub> -B <sub>7</sub> | Red, Green, and Blue data inputs. $R_0$ , $G_0$ , and $B_0$ are the least significant data bits. They are latched on the rising edge of CLOCK. Coding is binary. Unused inputs should be connected to either the regular PCB power or ground plane.                                                                                                                                                                                                                                                                                          |

| CLOCK                                                                                              | Clock input. The rising edge of CLOCK latches the $R_0$ - $R_7$ , $G_0$ - $G_7$ and $B_0$ - $B_7$ $\overline{SYNC}$ , $\overline{BLANK}$ , and REFWHITE inputs. It is typically the pixel clock rate of the video system. It is recommended that the CLOCK input be driven by a dedicated CMOS buffer.                                                                                                                                                                                                                                       |

| IOR,IOG,<br>IOB                                                                                    | Red, Green, and Blue current outputs. these high impedance current sources are capable of directly driving a doubly terminated $75\Omega$ co-axial cable. All outputs, whether used or not, should have the same output load (Note: A DC path to ground must be maintained).                                                                                                                                                                                                                                                                 |

| I <sub>SYNC</sub>                                                                                  | Sync current output. Typically this current output is directly wired to the IOG output, and enables sync information to be encoded onto the green channel. A logic '0' on the $\overline{\text{SYNC}}$ input results in no current being output to this pin, while logic '1' results in the following current being output: $I_{\text{SYNC}} \text{ (mA)} = 3468 \text{ X} \frac{V_{\text{REF}} \text{ (V)}}{R_{\text{SET}} \text{ (\Omega)}} = 111 \text{ LSBs}$                                                                            |

|                                                                                                    | If sync information is not required on the green channel, this output may be connected to V <sub>AA</sub> and the SYNC input tied high, causing the I <sub>SYNC</sub> current source to be turned off, reducing the power consumption.                                                                                                                                                                                                                                                                                                       |

| FS<br>ADJUST                                                                                       | Full scale adjust control. A resistor (R <sub>SET</sub> ) connected between this pin and AGND controls the magnitude of the full video signal (Fig. 3). The current flowing in the R <sub>SET</sub> resistor is equal to 32 LSBs. note that the IRE relationships in Fig. 3 are maintained, regardless of the full scale output current. The relationship between R <sub>SET</sub> and full scale current on IOG (assuming I <sub>SYNC</sub> is connected to IOG) is: $IOG (mA) = 12082 \ X \frac{V_{REF}(V)}{R_{SET}(\Omega)} = 387 \ LSBs$ |

|                                                                                                    | The full scale output current on IOR, IOB (mA) for a given R <sub>SET</sub> is defined as: $IOR, IOB (mA) = 8624 \text{ X} \frac{V_{REF} (V)}{R_{SET} (\Omega)} = 276 \text{ LSBs}$                                                                                                                                                                                                                                                                                                                                                          |

| COMP                                                                                               | Compensation pin. This pin provides compensation for the internal loop amplifier. A $0.01\mu F$ ceramic capacitor must be connected between this pin and the nearest $V_{AA}$ pin. Connecting the capacitor to $V_{AA}$ rather than to the AGND provides the highest possible power supply noise rejection.                                                                                                                                                                                                                                  |

| V <sub>REF</sub>                                                                                   | Voltage reference output. The output from an internal reference circuit, providing 1.2V (typical) reference.A $0.1\mu F$ ceramic capacitor must be used to decouple this output to $V_{AA}$ .                                                                                                                                                                                                                                                                                                                                                |

| AGND                                                                                               | Analog ground. All AGND pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>AA</sub>                                                                                    | Analog power. All V <sub>AA</sub> pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### **APPLICATION NOTES**

#### RS-343A and RS-170 Video Generation

For generation of RS-343A compatible video levels it is recommended that a doubly terminated  $75\Omega$  load be used with an  $R_{\text{SET}}$  resistor value of approximately 542 $\Omega$

Similarly for generation of RS-170-compatible video, it is recommended that a singly terminated  $75\Omega$  load be used with an  $R_{SET}$  value of about 774 $\Omega$ . If the VP101 is not driving a large capacitive load, there will be negligible difference in video quality between doubly terminated  $75\Omega$  and singly terminated 75Ω loads.t

If driving a large capacitive load (load RC >1/20 $\mathbf{H}f_c$ ) it is recommended that an output buffer with unloaded gain >2 be used to drive a doubly terminated 75 $\Omega$  load.

#### **COMP Resistor**

To optimise the settling time of the VP101, a resistor may be added in series between the COMP capacitor and COMP pin. The series resistor damps inductive ringing on COMP, thus improving settling time.

#### **Non-Video Applications**

The VP101 may be used in non-video applications by disabling the video specific control inputs. REF WHITE should be a logic '0' while BLANC and SYNC should be a logic '1'.  $I_{\mbox{\footnotesize SYNC}}$  should be connected to  $V_{\mbox{\footnotesize AA}}$  or AGND. All three outputs will have the same full scale output current.

The relationship between R<sub>SET</sub> and full scale output

current (I<sub>OLIT</sub>) in this configuration is as follows:

$$I_{out} \text{ (mA)} = 7968 \text{ X} \frac{V_{REF} \text{ (V)}}{R_{SET} \text{ (\Omega)}} = 255 \text{ LSBs}$$

Note that 1 LSB

$$\equiv \frac{V_{REF} (V)}{32 \text{ X R}_{SET} (\Omega)}$$

With the data inputs at \$00, there is a DC offset current (I<sub>min</sub>) defined as follows:

$$I_{min} \; (mA) = 656 \; X \; V_{REF} \; (V) \equiv 21 \; LSBs \\ \overline{R_{SET} \; (\Omega)} \label{eq:Imin}$$

Therefore the total full scale output current will be IOUT + I<sub>min</sub>. The REF WHITE input may optionally be used as a 'force to full scale' control.

#### **TIMING WAVEFORMS**

Fig.4 Input/output timing

- 1. Output delay, t<sub>DLY</sub>, measured from the 50% point of the rising edge of CLOCK to the 50% point of full scale transition.

- 2. Settling time,  $t_s$ , measured from the 50% point of full scale transition to the output remaining within  $\pm$  1 LSB.

- 3. Output rise/fall time, t<sub>VRF</sub> measured between the 10% and 90% points of full scale transition.

#### **PCB LAYOUT CONSIDERATIONS**

To obtain the optimum performance from the VP101 great care must be taken in the PCB layout to ensure low noise power and ground lines. This can be achieved by shielding the digital inputs and providing good decoupling.

#### **Power and Ground Planes**

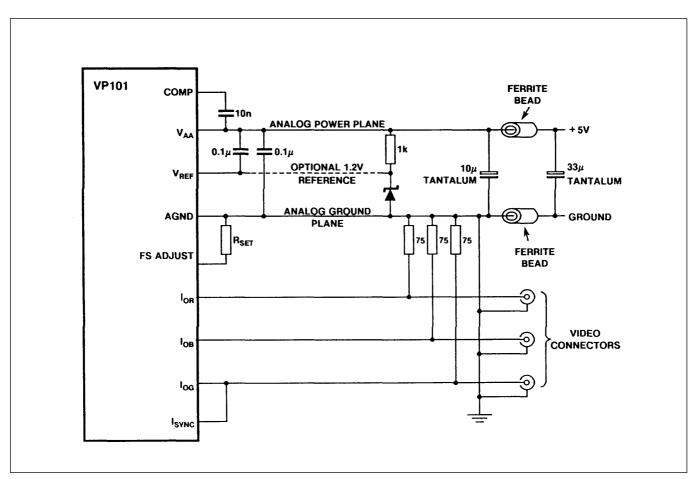

The VP101 and its associated circuitry should have its own power/ground planes connected at a single point through a ferrite bead. It is important that the regular PCB and ground planes do not overlay any portions of the analog power or ground planes to minimise plane-to-plane noise coupling.

#### **Digital Signal Interconnect**

The digital signal lines to the VP101 should be isolated as much as possible from the analog circuitry. Due to the high clock rates used, the clock lines to the VP101 should be as short as possible to minimise noise pickup.

Any pull-up resistors used on the inputs should be connected to the regular PCB power plane, not to the analog power plane.

#### **Supply Decoupling**

Noise on the analog power plane will be further reduced by the use of multiple decoupling capacitors (See Fig. 5).

Optimum performance is obtained with  $0.1\mu F$  chip ceramic capacitors placed as close as possible to the  $V_{AA}$  pins, with the shortest leads possible to reduce lead inductance.

It should be noted that while the loop amplifier circuitry of the VP101 will reject power supply noise, this rejection decreases with frequency. Any high frequency noise on the regular supply (such as produced by a switch mode power supplies) must be adequately suppressed, else the designer should consider using a three terminal regulator to supply the analog power plane.

#### **Analog Signal Interconnect**

For optimum performance the analog output connectors and source termination resistors should be as close as possible to the VP101 to minimise noise pickup and reflections due to impedance mismatch. The video out signals should overlay the ground plane and not the analog power plane, to maximise the high frequency power supply rejection.

Fig.5 VP101 typical connections

### HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom.

Tel: (01793) 518000 Fax: (01793) 518411

Fax: (408) 438 5576

#### **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02)66040993

- **JAPAN** Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023.

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UK, EIRE, DENMARK, FINLAND & NORWAY

Swindon Tel: (01793) 518510 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS3002 Issue No. 2.0 Feb 1994

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE